- 您现在的位置:买卖IC网 > Sheet目录362799 > EVAL-AD1833EB (Analog Devices, Inc.) Multichannel 24-Bit, 192 kHz, DAC

REV. 0

AD1833A

–6–

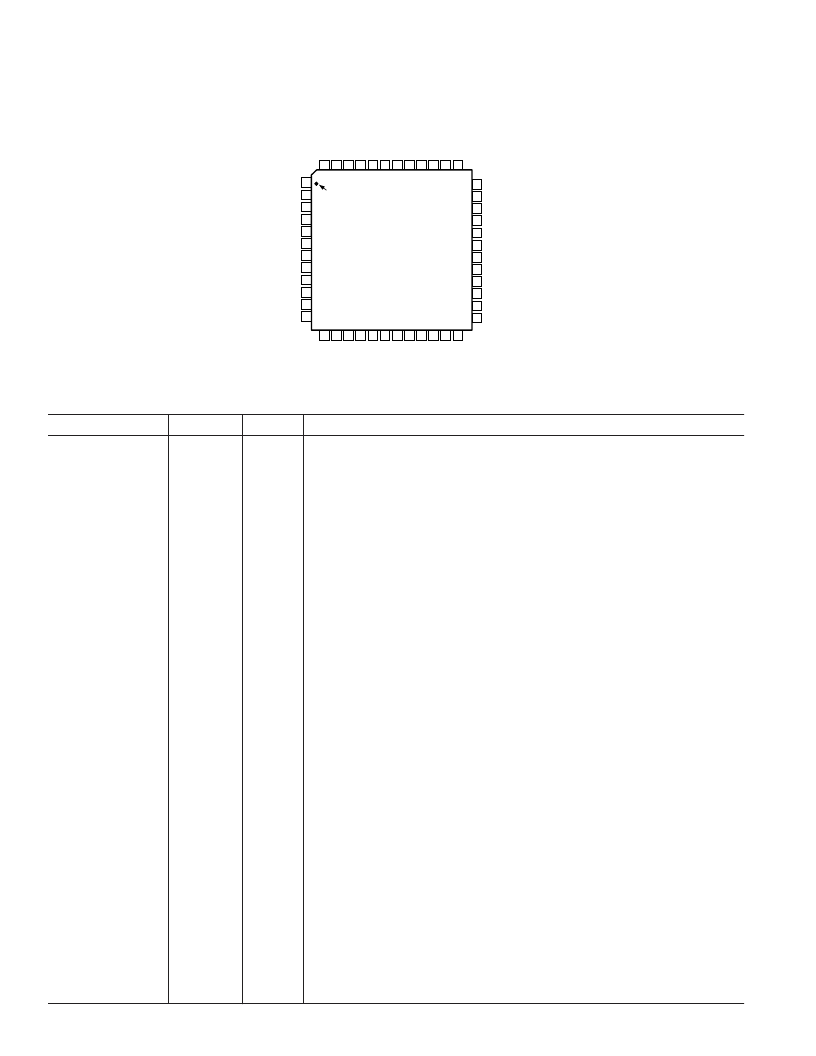

PIN CONFIGURATION

36

35

34

33

32

31

30

29

28

27

26

25

13 14 15 16 17 18 19 20 21 22 23 24

1

2

3

4

5

6

7

8

9

10

11

12

48 47 46 45 44

39 38 37

43 42 41 40

PIN 1

TOP VIEW

(Not to Scale)

OUTRP1

OUTRN1

AV

DD

AV

DD

AGND

AGND

AGND

DGND

DV

DD2

RESET

ZERO1L

ZERO1R

OUTLP1

OUTLN1

AV

DD

AV

DD

AGND

AGND

AGND

DGND

DV

DD1

ZEROA

ZERO3R

ZERO3L

AD1833A

O

O

O

O

A

D

F

F

A

O

O

O

O

Z

C

C

C

L

B

M

S

S

S

S

Z

PIN FUNCTION DESCRIPTIONS

Pin No.

Mnemonic IN/OUT

Description

1

2

3, 4, 33, 34, 44

5, 6, 7, 30, 31, 32, 41

8, 29

9

10

11

12

13

14

15

16

17

OUTLP1

OUTLN1

AV

DD

AGND

DGND

DV

DD1

ZEROA

ZERO3R

ZERO3L

ZERO2R

CLATCH

CDATA

CCLK

L/RCLK

O

O

DAC 1 Left Channel Positive Output.

DAC 1 Left Channel Negative Output.

Analog Supply.

Analog Ground.

Digital Ground.

Digital Supply to Core Logic.

Flag to Indicate Zero Input on All Channels.

Flag to Indicate Zero Input on Channel 3 Right.

Flag to Indicate Zero Input on Channel 3 Left.

Flag to Indicate Zero Input on Channel 2 Right.

Latch Input for Control Data (SPI Port).

Serial Control Data Input (SPI Port).

Clock Input for Control Data (SPI Port).

Left/Right Clock for DAC Data Input; FSTDM Input in TDM Slave Mode;

FSTDM Output in TDM Master Mode.

Bit Clock for DAC Data Input; BCLKTDM Input in TDM Slave Mode; BCLKTDM

Output in TDM Master Mode.

Master Clock Input.

Data Input for Channel 1 Left/Right (Data Stream Input in TDM and Packed Modes).

Data Input for Channel 2 Left/Right (L/RCLK Output to Auxiliary DAC in

TDM Mode).

Data Input for Channel 3 Left/Right (BCLK Output to Auxiliary DAC in TDM Mode).

Auxiliary I

2

S Output (Available in TDM Mode).

Flag to Indicate Zero Input on Channel 2 Left.

Flag to Indicate Zero Input on Channel 1 Right.

Flag to Indicate Zero Input on Channel 1 Left.

Power-Down and Reset Control.

Power Supply to Output Interface Logic.

DAC 1 Right Channel Negative Output.

DAC 1 Right Channel Positive Output.

DAC 2 Right Channel Negative Output.

DAC 2 Right Channel Positive Output.

DAC 3 Right Channel Negative Output.

O

O

O

O

I

I

I

I/O

18

BCLK

I/O

19

20

21

MCLK

SDIN1

SDIN2

I

I

I/O

22

23

24

25

26

27

28

35

36

37

38

39

SDIN3

SOUT

ZERO2L

ZERO1R

ZERO1L

RESET

DV

DD2

OUTRN1

OUTRP1

OUTRN2

OUTRP2

OUTRN3

I/O

O

O

O

O

I

O

O

O

O

O

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-AD1837EB

2 ADC, 8 DAC, 96 kHz, 24-Bit Codec

EVAL-AD1837AEB

2 ADC, 8 DAC, 96 kHz, 24-Bit Codec

EVAL-AD1838AEB

2 ADC, 6 DAC, 96KHZ 24 BIT CODEC

EVAL-AD1852EB

24-Bit Stereo DAC Evaluation Board

EVAL-AD1870EB

Single-Supply 16-Bit Stereo ADC

EVAL-AD1896EB

Automotive Low-Cost Non-Volatile FPGA Family; Voltage: 1.2V; Grade: -5; Package: Lead-Free ftBGA; Pins: 256; Temperature: AUTO; LUTs (k): 8

EVAL-AD1928EBZ

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

EVAL-AD1928EB

2 ADC/8 DAC with PLL, 192 kHz, 24-Bit Codec

相关代理商/技术参数

EVAL-AD1835AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1835EB

制造商:Analog Devices 功能描述:Evaluation Board For AD1835 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1836AEB

制造商:AD 制造商全称:Analog Devices 功能描述:Multichannel 96 kHz Codec

EVAL-AD1837AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1837EB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1838AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1838EB

制造商:Analog Devices 功能描述:Evaluation Board For 2 ADC, 8DAC 96 KHz, 24-Bit Sigma Delta Codec 制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk

EVAL-AD1839AEB

制造商:Analog Devices 功能描述:EVALUATION BOARD I.C. - Bulk